# Strukturelle Synthese von analogen Schaltungen

www.edacentrum.de/projekte/edaclusterforschung/aktuell/sams.html

#### Forschungskonsortium:

TU München ≪ TU Darmstadt ≪ Universität Frankfurt ≪ Fraunhofer EAS Dresden ≪

> Förderkennzeichen: 01 M 3070

Laufzeit des Vorhaben: 11/2003 bis 10/2006. Das SAMS-Projekt wurde im November 2003 gestartet und hat eine Laufzeit von drei Jahren. Das Forschungskonsortium setzt sich aus den Universitäten TU München. TU Darmstadt sowie Uni Frankfurt und dem Fraunhofer Institut Dresden zusammen. Dieser Bericht gibt einen Überblick über die Ziele und die Ergebnisse nach zwei Jahren Projektlaufzeit.

# **Motivation zum Projekt**

Die Struktursynthese ist eine der großen Herausforderungen in der EDA-Forschung für analoge Schaltungen. Der Analogentwurf ist durch eine Vielzahl von anwendungsspezifischen Entwurfsmethoden für sehr unterschiedliche Problemklassen gekennzeichnet. Je nachdem, ob z. B. einfache Operationsverstärker, Phasenregelschleifen, analog/digitale Blöcke wie Analog-Digital-Wandler oder komplexe Mixed-Signal-Systeme zu behandeln sind, werden während des Entwurfs unterschiedliche Abstraktionsebenen und Beschreibungsdomänen mit verschiedenen Modellierungssprachen durchlaufen. Derzeitige Arbeiten zur Entwurfsautomatisierung für analoge Schaltungen befassen sich vor allem mit der Dimensionierung und Wiederverwendung. Darüber hinaus werden aber dringend durchgängige Lösungsvorschläge für die Struktursynthese benötigt, die für den industriellen Einsatz geeignet sind.

# Ziele des Projekts

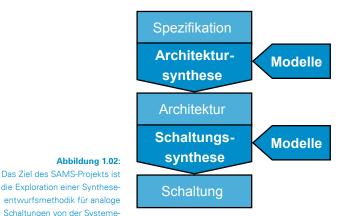

Dementsprechend ist das Ziel des Vorhabens SAMS mit seinen Arbeiten einen entscheidenden Beitrag für einen durchgängigen Struktur-Entwurfsprozess für analoge Schaltungen zu leisten. Die beteiligten Forschungseinrichtungen explorieren neue Entwurfstechnologien zur Top-Down-Synthese ausgehend von der Systemebene bis hin zur elektrischen Ebene (s. Abb. 1.02). Zur Validierung werden Schaltungsbeispiele industrieller Partner herangezogen.

Abbildung 1.02

Die Vernetzung unterschiedlicher Einzellösungen in Richtung einer geschlossenen Methodik steht dabei im Mittelpunkt. Die erforschten EDA-Methoden werden sowohl die Entwurfsproduktivität als auch die Entwurfsqualität deutlich steigern.

#### Themenschwerpunkte

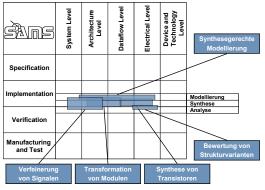

Das Projekt arbeitet auf den vier Abstraktionsebenen: System-, Architektur-, Datenfluss- und Schaltungsebene. Für die Synthese sind Werkzeuge zur Transformation und Verfeinerung von Blöcken und Signalen innerhalb und zwischen den beschriebenen Ebenen notwendig. Darüber hinaus müssen die Erzeugung einer Vielzahl von Transistorstrukturen, schnelle Bewertungsverfahren zur Lösungsraumexploration sowie eine synthesegerechte Modellierung in allen Hierarchien ermöglicht werden. Einen Überblick über die im Projekt behandelten Themen geordnet nach Abstraktionsebenen und den Phasen des Design-Flows zeigt Abb. 1.03.

Abbildung 1.03

### Architektursynthese

Für den ersten Syntheseschritt werden objektorientierte Modellierungsmethoden für die Verfeinerung von Architekturvarianten untersucht. Schwerpunkt liegt dabei auf der Untersuchung von Schnittstellen und Signalen von der Systemebene hin zur Architekturebene. Da auf Systemebene SystemC im starken Maße eingesetzt wird, werden u.a. auch Ansätze zur analogen Spracherweiterung betrachtet und dazu Lösungen vorgeschlagen. Die Hauptaufgabe liegt darin, Methoden zur interaktiven Verfeinerung und schnellen Bewertung unterschiedlicher Architekturvarianten zu erforschen. Für den nächsten Syntheseschritt werden Methoden zur Verfeinerung einer Architektur durch Transformation der Funktionsblöcke untersucht. Diese Verfeinerung basiert auf der Sprache VHDL-AMS, die zur Beschreibung von Modulen häufig eingesetzt wird. Ziel ist es, Methoden zu erforschen, mit denen die

# Abbildung 1.03:

Die Forschungsthemen des SAMS-Projekts konzentrieren sich auf die Modellierung, die Synthese und die Analyse von analogen Schaltungen - von der Systemebene bis zur elektrischen Ebene - wie sie in der edaMatrix dargestellt sind

die Exploration einer Syntheseentwurfsmethodik für analoge Schaltungen von der Systemebene auf die elektrische Ebene Spezifikationsabbildung anwendungsspezifisch gesteuert wird. Hierdurch ergibt sich auch ein Übergang von einer Schaltungsbeschreibung in SystemC-AMS auf VHDL-AMS.

#### Schaltungssynthese

Bei der Synthese und Bewertung von Architekturen werden Modelle mit syntheserelevanten Parametern benötigt, die in der Lage sind, Stabilitäts-, Robustheits- oder Genauigkeitsprobleme zu erkennen und zu beheben. Zu dieser synthesegerechten Modellierung müssen Methoden und Verfahren erforscht werden, die die notwendigen Informationen auf allen Ebenen zur Verfügung stellen und einen Austausch von syntheserelevanten Informationen zwischen den Ebenen erlauben. Damit wird die Möglichkeit geschaffen, physikalische Eigenschaften von der Transistorebene in die Architektur- und Systemebene zu transferieren.

Auf der Schaltungsebene werden Verfahren zur automatischen Topologiesynthese erforscht. Die Strukturen sollen durch systematisches Hinzufügen von Transistoren iterativ erzeugt, dimensioniert und bewertet werden. Hierzu werden Analyse- und Dimensionierungsverfahren im Projekt eingesetzt und erarbeitet. Ein weiterer Aspekt sind Verfahren zur schnellen Bewertung von Strukturvarianten. Mit ihrer Hilfe werden analoge Schaltungsstrukturen auf Transistorebene sehr schnell unter Berücksichtigung der verfügbaren Daten der Schaltungsspezifikation und Prozesstechnologie analysiert. Dies führt zu einer Beschleunigung des Entwurfsvorgangs und zu besseren Ergebnissen, da Entwurfsvarianten identifiziert werden, die ansonsten aus Zeitgründen nicht zur Bewertung gelangt wären.

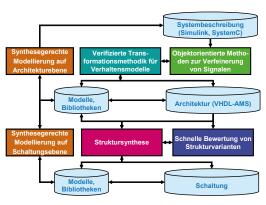

# Struktur des Projekts und der Arbeitspakete

Das Projekt teilt sich in zwei Arbeitspakete auf: Architektursynthese und Schaltungssynthese. Eine zusammenhängende Modellierung von der untersten bis zur obersten Ebene ermöglicht die iterative Verfeinerung der Modelle auf den oberen Ebenen durch Informationen aus der elektrischen Ebene. Abbildung 1.04 stellt die Projektbeiträge im Zusammenhang mit den Übergängen im Entwurfsprozess dar. Im Folgenden werden die Ergebnisse der Forschungsschwerpunkte dargestellt.

Abbildung 1.04

# Objektorientierte Methoden zur Verfeinerung von Signalen

Der Entwurf komplexer, heterogener Systeme beginnt in dem vorgestellten Entwurfsprozess mit einer ausführbaren Spezifikation. Ziel ist die interaktive Verfeinerung zu einer Architektur und die Verifikation bereits synthetisierter Schaltungen auf Systemebene. Hierzu werden Schaltungsmodelle genutzt, die aus einer Transistorbeschreibung erzeugt werden. (Siehe hierzu auch die Beschreibung zur synthesegerechten Modellierung.)

Problematisch ist bisher, dass zur Beschreibung von Spezifikation, Architektur und Schaltung ganz verschiedene Formalismen verwendet werden: Auf der System- und Architekturebene werden Modelle durch Transaktionen, gerichteten Signalfluss oder statischen Datenfluss beschrieben. Auf Schaltungsebene werden analoge Schaltungen durch elektrische Netzwerke und digitale Schaltungen durch ereignisdiskrete Modelle beschrieben. Eine Kopplung von Schaltungs- und Systemmodellen, wie sie beim interaktiven Entwurf, aber auch nach einer Synthese dringend zur Systemverifikation und Analyse benötigt werden, ist aufwändig und führt in der Regel zu Inkonsistenzen.

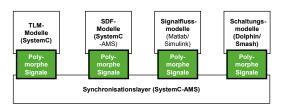

Die hier erarbeitete Lösung sieht die Einführung polymorpher Signale vor. Polymorphe Signale konvertieren implizit Signale zwischen unterschiedlichen Darstellungs- und Beschreibungsformen und überprüfen damit die Schnittstellen auf Konsistenz. So unterstützen sie das interaktive Austauschen von Teilen der ausführbaren Spezifikation oder eines Schaltungsmodells gegen Schaltungsvarianten. Sie können effizient für die Verfeinerung im Entwurfsprozess und die Verifikation durch die Simulation synthetisierter Schaltungen in einer System-Testbench eingesetzt werden.

# Prototyp - POLYSIGNAL

Zur Demonstration wurde auf Grundlage eines Prototyps von SystemC-AMS der Prototyp POLYSIGNAL entwickelt, der eine Kopplung von Modellen auf unterschiedlichen Abstraktionsebenen automatisiert. Da analoge Schaltungen nur begrenzt in SystemC-AMS simuliert werden können, wurde die interne Datenstruktur von polymorphen Signalen in das Shared Memory gelegt und damit eine Möglichkeit zur Anbindung externer Schaltungssimulatoren geschaffen. Damit wird der unmittelbare Austausch von abstrakten Blöcken durch Schaltungen ermöglicht, selbst wenn diese in unterschiedlichen Formalismen beschrieben sind und über eine unterschiedliche Anzahl von Ports verfügen. Zu Demonstrationszwecken wurde Dolphin/ SMASH über polymorphe Signale mit SystemC-AMS gekoppelt; eine Anbindung von Matlab/Simulink wird angestrebt (s. Abb. 1.05).

#### Industriepartner und Förderer:

- >> AMD Saxony LLC&Co. KG

- >> Atmel Germany GmbH

- >> Bundesministerium für Bildung und Forschung (BMBF)

- Cadence Design Systems GmbH

- >> Deutsches Zentrum für Luftund Raumfahrt (DLR)

- » Deutsche Thomson-Brandt GmbH

- >> edacentrum

- >> Infineon Technologies AG

- >> Lucent Technologies Network Systems GmbH

- » Melexis GmbH

- >> MunEDA GmbH

- >> Nokia GmbH

- >> PDF Solutions GmbH

- >> Robert Bosch GmbH

- >> Philips Semiconductors GmbH

- >> X-FAB Semiconductor Foundries AG

# Abbildung 1.04:

Im vorgeschlagenen Analogsynthese-Flow wird eine schrittweise Verfeinerung von der Systemebene, über die Architekturebene, der Übergang zu konservativen Signalen sowie die Verfeinerung und Analyse auf elektrischer Ebene vorgeschlagen.

# Abbildung 1.05: Mit Hilfe von polymorphen Signalen und Simulatorkopplungen werden Module in verschiedenen Sprach- und Modellierungsformen zu einem simulationsfähigen Systemmodell verbunden

Abbildung 1.05

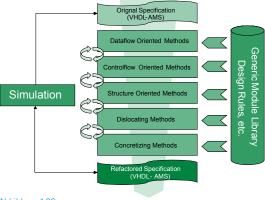

# Transformationsgestützte Methodik zur Vorbereitung der Struktursynthese analoger Schaltungen

Ziel der Analogsynthese auf Architekturebene ist die Erforschung von Verfeinerungsverfahren von Schaltungsmodulen. Der grundlegende Algorithmus hierfür baut auf drei generischen Verfahren auf, die als Schnittstellenumwandlung, Code Refactoring und ODAE Partitionierung bezeichnet werden (ODAE: Gewöhnliche Differential-Algebraische Gleichungen). Die Schnittstellenumwandlung dient vorwiegend der Abbildung von Interface-Beschreibungen nichtkonservativer Signalflussmodelle auf die entsprechenden Schnittstellen von konservativen Verhaltensmodellen. Eine Datenstruktur für den Übergang zwischen beiden Modellklassen in VHDL-AMS wurde hierfür festgelegt. Das Code Refactoring besteht aus einer Abfolge von Modelltransformationen, die das prinzipielle Verhalten des Modells nicht verändern (s. Abb. 1.06).

Abbildung 1.06:

Das Refactoring ermöglicht eine

Verfeinerung der Module in

synthetisierbare Funktionsblöcke sowie die Umwandlung

auf elektrische Signale

Abbildung 1.06

# Abbildung 1.07: Die Struktursynthese nutzt eine Datenbank mit Syntheseregeln, um aus Grundbausteinen eine Blockkette zu erstellen, die sich in eine dimensionierte Topologie umwandeln lässt

Dadurch wird die Synthetisierbarkeit der vorhandenen, zunächst abstrakten Modellbeschreibung erreicht. Die Verfeinerung der Modellbeschreibungen mittels Code Refactoring ist eine notwendige Vorstufe zur eigentlichen Struktursynthese. Die ODAE Partitionierung dient der eigentlichen Durchführung der Struktursynthese analoger Schaltungen. Sie transformiert eine mittels Gleichungssystemen notierte, abstrakte Verhaltensspezifikation eines Entwurfsobjektes in eine entsprechende, zunächst noch grobkörnige strukturelle Repräsentation.

Ein Systemmodell, dessen Verhalten in einer analogen Modellierungssprache (wie VHDL-AMS) notiert ist, wird während der Synthese zunächst syntaktisch und semantisch überprüft und in einen entsprechenden Parserbaum abgebildet. Dieser Parserbaum enthält die vollständige Informationsstruktur des Modells. Zur leichteren Manipulation dieser Datenstruktur wird

ein Zwischenformat eingeführt, das als Objektbaum bezeichnet wird. Dadurch lassen sich Refactoring-Algorithmen effizienter implementieren und ausführen. In der aktuellen Implementierung der Methodik werden die Software-Werkzeuge ANTLR und Castor XML verwendet. Basierend auf dem so konstruierten Parserbaum werden die Methoden zur Schnittstellenumwandlung, Code Refactoring und zur ODAE Partitionierung nacheinander eingesetzt, um das Modell einer analogen Schaltung umzustrukturieren, zu verfeinern und zu vereinfachen. Das Ergebnis ist eine detaillierte Modellbeschreibung, die als Eingabe für die eigentliche Struktursynthese von Funktionsblöcken auf der Transistorebene Verwendung findet.

#### Prototyp - RAMS

Die genannte Methodik wurde als das CAE-Werkzeug RAMS prototypisch implementiert. Als Programmiersprache wird Java zusammen mit der Entwicklungsumgebung IDE Eclipse verwendet. Die neu entwickelte Methodik unterstützt den Top-down Entwurfsablauf, der die Abstraktionshierarchie von der Systemspezifikation bis hin zur Transistornetzliste traversiert. Erste Forschungsergebnisse wurden bereits publiziert und fanden international Beachtung.

# Struktursynthese von Analogschaltungen auf Transistorebene

Es wird ein Verfahren zur Topologiesynthese analoger Schaltungen erforscht. Bei der Synthese auf Transistorebene kommt der hierarchischen Realisierung einer Schaltung aus Transistorgruppen (z.B. Stromspiegel, Differenzpaar), hier Funktionsblöcke genannt, eine große Bedeutung zu. Das Syntheseverfahren nutzt eine hierarchische Datenbank, in der analoge Grundbausteine und die entsprechenden Basisblöcke, sowie eine Reihe von Syntheseregeln (s. Abb. 1.07) abgelegt sind.

Abbildung 1.07

In einem Kompositionsverfahren werden Funktionsblöcke aus den zusammengeschalteten Grundbausteinen in einer Blockkette aufgebaut. Die Syntheseregeln geben dabei die Anordnung der Grundbausteine vor. Verschiedene Ausführungen der Grundbausteine sowie deren Dimensionierung ermöglichen die systematische Erzeugung einer großen Vielzahl von Schaltungsvarianten, die einen großen Suchraum abdecken. Diese Vorgehensweise erlaubt eine gute Einschränkung des Suchraums. Allerdings sind nach Dimensionierung und Simulation erfahrungsgemäß nur einige wenige Strukturen überhaupt zur Erfüllung der Funktion geeignet. Deshalb wird die symbolische Analyse als ein Bewertungsmechanismus genutzt, die möglichst alle nicht dimensionierbaren oder nicht sinnvollen Schaltungen eliminiert. Im Falle einer linearen Übertragungsfunktion

kann durch ein stark vereinfachtes Transistormodell eine sehr gute Analyse durchgeführt werden. Die Ergebnisse der Analyse werden dann mit der aus der Spezifikation als Constraint vorhandenen Übertragungsfunktion verglichen. Dieses Vorgehen kann auch auf nichtlineare Übertragungsfunktionen (im Zeitbereich) erweitert werden.

Die endgültige Dimensionierung der Funktionsblöcke erfolgt durch das Software-Paket WiCkeD von MunEDA. Damit konnte gezeigt werden, dass die Spezifikation mit ihren Randbedingungen mit der synthetisierten Schaltung erfüllt wurde. Erste Ergebnisse mit Operationsverstärkern zeigen, dass dieses Verfahren für die Industrie einsetzbar ist. Weitere Untersuchungen werden den Einsatz bei anderen analogen Funktionsblöcken prüfen, um somit das Synthesewerkzeug auf eine breitere Basis zu stellen.

# Prototyp ASS – Analoge Struktursynthese anhand eines Operationsverstärkers

Der entwickelte Prototyp ASS ermöglicht die Struktursynthese und Identifizierung geeigneter Schaltungen. Als Beispiel wird eine Synthese einer Schaltung mit einer Differenzspannung als Eingang und einer Spannung als Ausgang gewählt. Solche Schaltungen werden meistens als Operationsverstärker verwendet und eignen sich wiederum zur Erzeugung von Addierern, Differenzierern und Integratoren. Die Blockkettengröße ist auf 4 Blöcke begrenzt. Im Struktursyntheseschritt sind insgesamt 448 Blockketten, d.h. 2732 Schaltungen, ausgegeben. Durch symbolische Analyse werden die Schaltungen analysiert und evaluiert. Durch den Einsatz von Performance-Kriterien werden 50 Schaltungen als geeignet ausgewählt. Das Resultat ist eine Schaltung mit einer Verstärkung von 81,3 dB und einer Grenzfrequenz von 1 MHz.

# Schnelle Bewertung von Strukturvarianten analoger Schaltungen

Bei der Synthese einer analogen Schaltung bzw. einer analogen Komponente kommt zwischen der Synthese der Schaltungsstruktur auf Transistorebene und der Synthese des Layouts für die Fertigung ein Zwischenschritt im Entwurfsablauf hinzu: die Dimensionierung von einstellbaren Parametern wie beispielsweise die CMOS-Transistorweiten. Die Dimensionierung spielt eine entscheidende Rolle, da erst mit ihr die tatsächlichen Schaltungseigenschaften feststehen. Bei der Synthese einer Schaltungsstruktur müssen üblicherweise sehr viele, manchmal Tausende von Strukturvarianten verglichen werden, bevor eine geeignete Schaltungsstruktur gefunden ist. Bei diesen Vergleichen müssen auch die Schaltungseigenschaften einbezogen werden, was eine Dimensionierung voraussetzt. Die Dimensionierung muss sowohl das Nominalverhalten als auch das Toleranzverhalten hinsichtlich der Schaltungsspezifikationen und der gegebenen Betriebs- und Produktionstoleranzen erfassen. Eine solch ausführliche Dimensionierung ist extrem simulationsintensiv und zeitaufwändig und kommt daher für die Struktursynthese nicht in Frage.

Ziel ist es hier, Verfahren zu erforschen, mit denen analoge Schaltungsstrukturen auf Transistorebene besonders schnell analysiert werden können. Gelingt dies, wird auf diese Weise zum ersten Mal ermöglicht, eine sehr große Anzahl von Strukturvarianten zu betrachten, u.a. auch Varianten, die zuvor aus Aufwandsgründen nicht hätten berücksichtigt werden können.

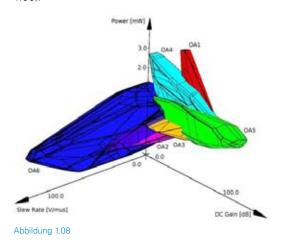

Die Leistungsfähigkeit einer Schaltungsstruktur wird durch die Menge der Eigenschaftswerte beschrieben, die sich durch gültige, d.h. technisch sinnvolle Dimensionierungen einstellen lassen. Diese Menge wird realisierbarer Eigenschaftsraum genannt. Gegenwärtig konzentrieren sich alle Verfahren darauf, nur eine kleine Anzahl besonders wichtiger Eigenschaften, meist zwei oder drei, zu benutzen, um den Aufwand gering zu halten. Allerdings werden viele analoge Funktionsblöcke erst durch weit mehr Eigenschaften hinreichend beschrieben. Daher wird in diesem Projekt eine neue simulations basierte Methode erforscht und prototypisch implementiert, die dank eines linearen Ansatzes eine hohe Anzahl von Eigenschaften gleichzeitig behandeln kann. Als Resultat ergibt sich eine formale Approximation und Visualisierung des realisierbaren Eigenschaftsraumes in Form eines Polytops (s. Abb.

Abbildung 1.08: Mit Hilfe einer 3D-Visualisierung ist eine schnelle Analyse des Eigenschaftsraums der Schaltung möglich

# Prototypen - Analog Performance Explorer

Analog Performance Explorer ist eine Java3D-basierte Software zur Visualisierung von zwei- und drei-dimensionalen Polytopen, mittels derer der erreichbare Eigenschaftsraum eines analogen Schaltungsblocks abgeschätzt wird. Anwendungen sind die Evaluierung und Selektion von Schaltungsstrukturen.

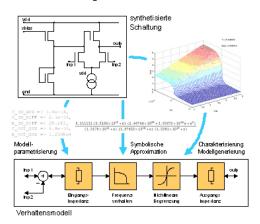

# Modellierung und Simulation für die Synthese von Analog- und Mixed-Signal-Schaltungen

Ein wichtiger Bestandteil eines durchgängigen Syntheseablaufes für analoge Schaltungen ist die Modellierung. Sie dient der Abstraktion des Schaltungsverhaltens auf höheren Hierarchieebenen. Damit ist es möglich, die Erreichung des Entwurfsziels auch innerhalb eines komplexeren Systems zu überprüfen und schnell eine große Zahl von Variantensimulationen innerhalb des Entwurfsraumes auf hoher Abstraktionsebene mit notwendiger Genauigkeit und noch akzeptablerer Performance durchzuführen. Auch wird hierdurch die Optimierung der Ressourcenverteilung auf Systemebene ermöglicht.

Im Verlaufe der Architektursynthese werden aus algorithmischen Systemmodellen Strukturen auf Blockebene erzeugt. Werden nun zu den einzelnen Blöcken Schaltungstopologien synthetisiert oder aus einer vorhandenen Bibliothek ausgewählt, können mit Hilfe der Modellierung Parameter und Kennlinien zu diesen Blöcken ermittelt werden. Damit lassen sich die Strukturmodelle parametrieren und verfeinern. Es stehen realistische Werte und Abhängigkeiten auf der Blockebene bereit, die eine wesentlich exaktere Untersuchung des Entwurfsraumes einer Architektur und den Vergleich verschiedener Entwurfsvarianten ermöglichen. Für die Integration der Modellierung in einen weitgehend automatisierten Syntheseablauf ist ebenfalls ein hoher Automatisierungsgrad für die Ermittlung von Modellparametern und der Modellgenerierung notwendig. Die verschiedenen Modellierungsverfahren unterscheiden sich in ihren Eigenschaften bezüglich der Eignung für einen automatisierten Modellierungsablauf.

Das Wissen über Zusammenhänge auf der Schaltungsebene (Abhängigkeiten zwischen Parametern, Berücksichtigung parasitärer Effekte) wird mittels Modellierung auf ein höheres Abstraktionsniveau transformiert, um die dort anstehenden Entwurfsentscheidungen fundierter treffen zu können. Die Synthese von analogen und Mixed-Signal-Schaltungen ist kein reiner Top-Down-Prozess, der ausschließlich von höheren zu niedrigeren Abstraktionsebenen verläuft, sondern er schreitet in iterativen Schleifen innerhalb der Ebenen und ebenenübergreifend fort. Im Projekt werden analytische, numerische und symbolische Modellierungsverfahren im Hinblick auf die Unterstützung der Analogsynthese untersucht, bewertet und am Beispiel getestet.

Symbolische Modellierungsmethoden gehören zur Klasse der konstruktiven Verfahren. Diese gehen direkt von der Struktur des nachzubildenden Systems aus. Das Modellierungsprinzip besteht darin, das vollständige Gleichungssystem einer Schaltung zu vereinfachen. Dabei wird eine Fehlerschranke vorgegeben, bis zu der die Simulation der Beschreibungsgleichungen des Modells von den Ergebnissen der Schaltungssimulation abweichen darf. Demzufolge ist das entstehende Modell von der Wahl des Simulationsbereiches und der Fehlerschranken für die Vergleichssimulation abhängig. Neben der symbolischen Analyse im Kleinsignalbereich können auch Verfahren zur Approximation im Zeitbereich von den Werkzeugen eingesetzt werden, wie sie beispielsweise für die Analyse von Oszillatoren notwendig sind.

Die numerische Modellierung kann nahezu beliebige Zusammenhänge zwischen verschiedenen Entwurfsund Einflussgrößen ermitteln und in ein Modell einbringen. Dabei muss die innere Struktur des Modells nicht bekannt sein, deshalb spricht man hier von "Black-Box-Verfahren". Wichtiges Hilfsmittel hierzu ist die Charakterisierung, bei der durch Simulation Kennfelder ermittelt und Parameter extrahiert werden. Damit können die Abhängigkeiten erfasst und entweder direkt im Modell als Tabelle abgelegt oder über den Zwischenschritt einer Approximation mittels Ansatzfunktion nachgebildet werden. Diese Verfahren eignen sich sehr gut für eine Automatisierung und unterliegen nicht den Komplexitätsgrenzen der symbolischen Modellierung. Allerdings ersetzt das entstehende Modell jeweils nur die eine charakterisierte Schaltung innerhalb des gewählten Parameterbereiches. Außerdem sind mehrdimensionale Tabellenmodelle in der Abarbeitung aufwändig wegen der Interpolation zwischen den Stützstellen.

Bei der Modellierung mit analytischen Ansatzfunktionen wird ein parametrisierbares Verhaltensmodell einmalig für eine Schaltungsklasse angelegt, dessen freie Parameter durch Charakterisierung einer Schaltung bestimmt werden. Ebenso werden parametrierbare Verhaltensmodelle durch ideale SPICE-Ersatzelemente beschrieben. Für die Erstellung des Modells ist grundsätzliches Wissen über Aufbau und Wirkungsweise der Schaltung erforderlich, während die konkreten Parameter numerisch bestimmt werden. Diese Charakterisierung und Modellgenerierung kann wiederum automatisch erfolgen.

Abbildung 1.09

Abb. 1.09 zeigt die gemeinsame Verwendung der verschiedenen Modellierungsverfahren am Beispiel einer im Projekt synthetisierten Schaltung. Die Eingangsimpedanz des Modells wird mit charakterisierten Werten parametriert. Mittels symbolischer Verfahren wird die Übertragungsfunktion bestimmt. Ein numerisches Modell approximiert die nichtlineare Ausgangsspannungsbegrenzung in Abhängigkeit von der Betriebsspannung.

Verhaltensmodelle können sehr effizient in der Simulation und Synthese eingesetzt werden. Entscheidend

Abbildung 1.09:

Ein Schaltungsmodell für die

Nutzung auf den höheren Abstraktionsebenen

bei der Modellierung hier ist die Berücksichtigung von syntheserelevanten Parametern auf allen Abstraktionsebenen. Dadurch lassen sich in jedem Schritt der Verfeinerung syntheserelevante Entscheidungen treffen und optimieren.

# Prototyp - Chameleon

Für die Umsetzung automatisierbarer Modellierungsschritte wurde der Software-Prototyp Chameleon (Characterization and Modeling Environment) erstellt. In diese offene Modellierungsplattform werden geeignete Verfahren und Werkzeuge integriert, die der Charakterisierung, Modellgenerierung und Modellparametrisierung zur Steuerung der Synthese dienen.

#### Resümee

Dieses Projekt wird vom BMBF, der DLR und dem edacentrum, sowie einem Industriekonsortium finanziell und fachlich unterstützt . Das Forschungskonsortium möchte mit seiner Expertise die Firmen unterstützen, die industrielle Entwurfsmethodik für analoge Schaltungen zu verbessern.

Mit den Ergebnissen nach zwei Jahren Projektlaufzeit deutet sich an, dass der vom Projekt eingeschlagene Weg zur Synthese analoger Schaltungen zukunftsweisend bei der Verbesserung der Entwurfsmethodik in Forschung und Anwendung sein kann. Es ist jedoch nur ein erster Schritt. Weitere Anstrengungen sind notwendig, um die ersten schmalen Wege eines durchgängigen Syntheseprozesses für analoge Schaltungen auf eine breite und industrierelevante Basis zu stellen. Dies geht nur in enger Zusammenarbeit mit der Anwenderindustrie. (VS)

# SAMS-Literatur

P. Schwarz, V. Schöber, "Specification and Modelling of Analog Circuits - What are the needs of a synthesis driven approach?", FDL, 2003

Ralf Popp , "Dem Analog-Entwickler das Leben erleichtern", Elektronik, 23, 2003

- S. Huss, S. Klupsch, "A new approach to mixed-signal model refinement by code Refactoring methods", FDL, 2003

- J. Romberg and C. Grimm, "Refinement of Hybrid Systems from Formal Models to Design Languages", Languages for System Specification, Kluwer Academic Publisher, C. Grimm (editor), 2004

- A. Vachoux, C. Grimm, and K. Einwich, "Towards Analog and Mixed-Signal SoC Design with SystemC-AMS", IEEE International Workshop on Electronic Design, Test and Applications (DELTA), Perth, Australia, 2004

- C. Grimm, W. Heupke, C. Meise, and K. Waldschmidt, "Refinement of Mixed-Signal Systems with Affine

Arithmetic", Design and Test in Europe 2004 (DATE), Paris, 2004

Rüdiger Schroll, Christoph Grimm, Klaus Waldschmidt, "HEAVEN: A Framework for the Refinement of Heterogeneous Systems", FDL, Lille, France, 2004

G. Stehr, H. Graeb, K. Antreich, "Analog performance space exploration by Fourier-Motzkin Elimination with application to hierarchical Sizing", IEEE/ACM International Conference on Computer-Aided Design (ICCAD), USA. 2004

Kaiping Zeng, Sorin A. Huss, "RAMS: A VHDL-AMS Code Refactoring Tool Supporting High Level Analog Synthesis", University Booth at DATE'2005, Munich, Germany, 2005

- R. Jancke, S. Böhme, Ch. Clauss, Th. Halfmann, P Schwarz, R. Sommer, P. Trappe, "Modellierungsunterstützung für Mixed-Signal-Systeme durch symbolische Vereinfachung nichtlinearer Blöcke", ANALOG, Hannover, 2005

- G. Stehr, H. Graeb, K. Antreich, "Ein linearer Ansatz zur effizienten Abschätzung der Leistungsfähigkeit analoger Schaltungen", ANALOG, Hannover, 2005

- R. Schroll, C. Grimm, and K. Waldschmidt, "Verfeinerung von Mixed-Signal Systemen mit polymorphen Signalen", ANALOG, Hannover, 2005

- C. Grimm, W. Heupke, and K. Waldschmidt, "Analysis of Mixed-Signal Systems with Affine Arithmetic", IEEE Transactions on Computer Aided Design of Circuits and Systems, (1), 2005

Kaiping Zeng, Sorin A. Huss, "RAMS: A VHDL-AMS Code Refactoring Tool Supporting High Level Analog Synthesis", IEEE COMPUTER SOCIETY ANNUAL SYMPOSIUM ON VLSI, Tampa, Florida, USA, 2005

- C. Grimm, R. Schroll and K. Waldschmidt, "Refinement of Mixed-Signal Systems: Between HEAVEN and HELL", Advances in Design and Specification Languages for SoCs. Kluwer Academic Publisher, 2005

- D. Mueller, G. Stehr, H. Graeb, U. Schlichtmann, "Deterministic Approaches to Analog Performance Space Exploration", ACM/IEEE Design Automation Conference (DAC), 2005

- D. Müller, G. Stehr, H. Gräb, U. Schlichtmann, "Eigenschaftsraumexploration bei der hierarchischen Dimensionierung analoger integrierter Schaltungen", Workshop "Entwurfsmethoden für Nanometer VLSI Design", 35. Jahrestagung der Gesellschaft für Informatik, Bonn, 2005

# Weitere Informationen:

http://www.em.cs.unifrankfurt.de/sams

## Kont@kt:

Dr.-Ing. Volker Schöber edacentrum Schneiderberg 32 30167 Hannover fon: 0511 762-19688 schoeber@edacentrum.de