edacentrum | Schneiderberg 32 | 30167 Hannover | fon: +49 511 762-19699 | email: info edacentrum [dot] denach oben

edacentrum [dot] denach oben

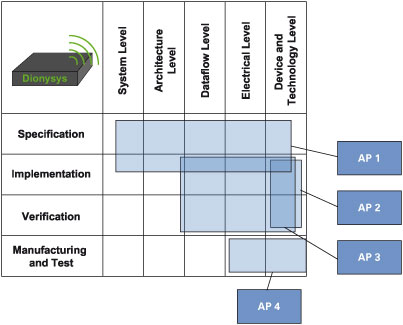

Im Gegensatz zum System-on-Chip-Entwurf (SoC) ist für den System-in-Package-Entwurf (SiP) bisher keine durchgängige Entwurfsmethodik vorhanden, die einen schnellen, sicheren und qualitätsgerechten Entwurf ermöglicht. Damit zukünftige Entwurfsprojekte nicht an der mangelnden Entwurfsunterstützung scheitern, haben sich die genannten Partner unter dem Dach des BMBF zu einem gemeinsamen Forschungsprojekt zusammengeschlossen. Das Ziel ist, die ganzheitliche Betrachtung des im Gehäuse integrierten Systems unter Einschluss der Hochfrequenz (HF)-Teile zu ermöglichen und die schnelle und sichere Umsetzung in ein zuverlässig arbeitendes SiP zu garantieren. Themen des Projekts sind unter anderem die technologieübergreifende Systemkonzeption, Einbindung der elektromagnetischen Simulation zur Analyse von HF- und Gehäusestrukturen, eine automatisierte Generierung passiver HF-Bauelemente, sowie die Beherrschbarkeit des Tests dieser hochkomplexen Systeme.

Projektkoordination:Infineon Technologies AG Projektmanagement:Fraunhofer Institut für Integrierte Schaltungen (IIS) Projektpartner:

Forschungspartner:

Förderkennzeichen:BMBF F&E 01M3084 Laufzeit:01.07.2007 - 30.06.2010 Webseite: | Projekt-InformationenSchlussbericht |

| Abkürzung | Bedeutung |

|---|---|

| PB | Projektbericht |

| PKB | Projektkurzbericht |

| PN | Projektnachricht |

| PSB | Projektschlussbericht |